Overview of Data Bus

The data bus is an essential component of a computer system that allows the transfer of data between different parts of the system. It serves as a pathway or communication channel through which information travels from one component to another. In simple terms, the data bus acts as a conduit that enables the exchange of data between the processor, memory, and input/output devices.

Without a data bus, the various components of a computer system would be unable to communicate with each other, rendering the system useless. The data bus ensures a smooth flow of information, enabling efficient and timely data transfers within the system.

The data bus is a crucial element in both the internal and external communications of a computer system. Internally, it allows for the exchange of data between the CPU (Central Processing Unit), memory, and other internal components. Externally, it facilitates data transfer between the computer system and peripherals such as keyboards, mice, printers, and storage devices.

One of the key characteristics of a data bus is its width, which refers to the number of lines or wires it has. The width determines the amount of data that can be transmitted simultaneously. For instance, an 8-bit data bus can transfer 8 bits of data in parallel, while a 16-bit bus can handle 16 bits at a time.

The data bus operates on a clock signal, which synchronizes the transfer of data between the sender and receiver. When the clock signal cycles, the data on the bus is read or written by the respective components. The speed at which the data bus operates is measured in bits per second (bps) or megahertz (MHz).

What is a Data Bus?

A data bus is a communication pathway or channel within a computer system that enables the transfer of data between various components. It serves as a vital link between the processor, memory, and input/output devices, allowing for the seamless movement of information.

Think of the data bus as a highway where data travels from one destination to another. It carries binary information in the form of electrical signals, utilizing a set of wires or lines to transmit and receive data.

The primary purpose of a data bus is to facilitate data transfer between different components of the computer system. It acts as a shared pathway through which the processor, memory, and other hardware devices can exchange information.

The data bus operates on the principle of parallel communication, meaning that multiple bits of data are transferred simultaneously. This significantly speeds up the data transfer process and enhances the overall performance of the system.

Typically, the data bus is categorized based on its width, which represents the number of wires or lines it contains. The width determines the number of bits that can be transmitted simultaneously. A wider data bus allows for faster data transfer rates, as more bits can be sent or received in a single cycle.

In addition to its width, the data bus is also characterized by its speed. The speed of a data bus is measured in bits per second (bps) or megahertz (MHz) and determines how quickly data can be transferred between the components of the computer system.

The data bus plays a crucial role in ensuring the smooth operation of a computer system. By providing a dedicated pathway for data transfer, it allows for efficient communication between the various hardware components. Without a data bus, the components would be unable to exchange information, leading to a breakdown in functionality.

Importance of Data Bus in Computer Systems

The data bus is a critical component in computer systems, providing a vital link that enables efficient communication and data transfer between different hardware components. Its importance lies in the following key aspects:

1. Data Transfer: The data bus allows for the seamless transfer of data between the processor, memory, and input/output devices. It ensures that information can be exchanged quickly and accurately, enabling the proper functioning of the system.

2. Parallel Communication: The data bus operates on the principle of parallel communication, where multiple bits of data are transferred simultaneously. This parallelism significantly increases the speed and efficiency of data transfer, optimizing the overall system performance.

3. System Integration: The data bus acts as a means of integrating various hardware components within the computer system. It provides a standardized interface that allows different devices to communicate with each other, ensuring compatibility and interoperability.

4. Memory Management: The data bus plays a crucial role in managing memory operations within a computer system. It facilitates the transfer of data between the processor and memory, allowing for the retrieval and storage of information as required by the system.

5. Input/Output Operations: The data bus enables data transfer between the processor and input/output devices such as keyboards, mice, printers, and storage devices. It allows for the exchange of data between the system and these external peripherals, enabling user interaction and data storage.

6. System Performance: The efficient operation of the data bus is essential for maintaining overall system performance. A robust and properly designed data bus ensures that data transfer is fast, reliable, and synchronized, reducing latency and enhancing the responsiveness of the system.

7. Scalability and Upgradability: The data bus provides a scalable platform for system expansion and future upgrades. By adhering to industry-standard protocols and interfaces, it allows for the integration of new components and technologies, ensuring the system’s flexibility and adaptability.

Overall, the data bus is of utmost importance in computer systems as it enables effective communication and data transfer between various hardware components. It contributes to the overall performance, functionality, and expandability of the system, ensuring a smooth and efficient computing experience.

Different Types of Data Bus

The data bus in a computer system can be classified into different types based on various factors, including its width, direction of data flow, and purpose. Understanding these different types of data bus is crucial in comprehending how data is transmitted within a computer system. Here are the most commonly used types:

1. System Bus: The system bus is the primary data bus in a computer system and is responsible for communication between the processor and memory. It consists of three main buses: the data bus, address bus, and control bus. These buses work together to facilitate data transfer and control operations within the system.

2. Address Bus: The address bus is a unidirectional bus that carries the memory addresses required for reading from or writing to specific locations in memory. It determines the location of the data being transferred and is used by the processor to communicate with memory and input/output devices.

3. Data Bus: The data bus is a bidirectional bus that carries the actual data being transferred between the processor, memory, and input/output devices. It allows for parallel communication, transmitting multiple bits of data simultaneously across its lines. The width of the data bus determines the number of bits that can be transmitted simultaneously.

4. Control Bus: The control bus is a bidirectional bus that carries control signals necessary to coordinate and regulate data transfer and operation of the computer system. It carries signals such as read/write signals, interrupt signals, and clock signals, ensuring synchronization and control of various system components.

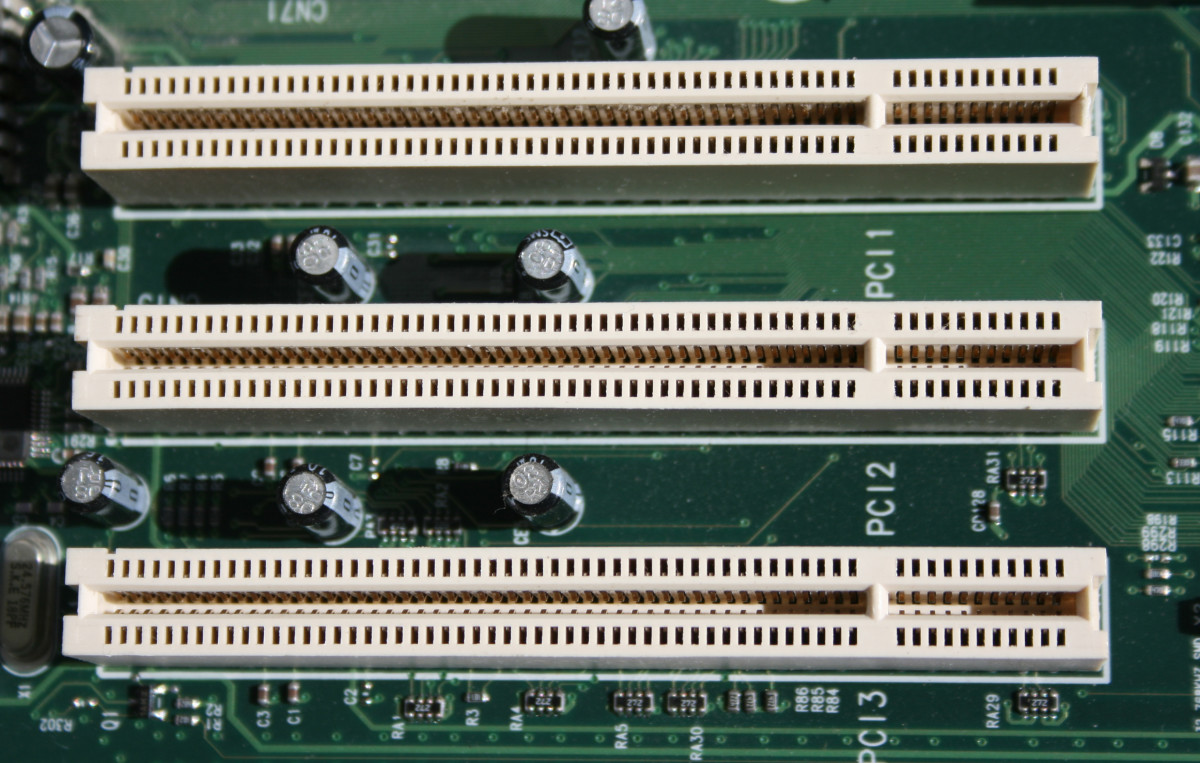

5. Expansion Bus: The expansion bus is responsible for connecting peripheral devices to the computer system. It allows for the addition of new hardware components, such as graphics cards, network cards, and sound cards, to enhance system functionality. Common expansion bus standards include PCI (Peripheral Component Interconnect) and PCIe (PCI Express).

6. Local Bus: The local bus is a high-speed data bus that connects the processor directly to the memory cache. It allows for faster data transfer, as it bypasses the system bus and directly links the CPU with the cache memory. Local buses, such as the front-side bus (FSB), facilitate efficient communication between the CPU and cache, enhancing system performance.

7. Backplane Bus: The backplane bus is used in large-scale computer systems, such as servers and mainframes, that require multiple interconnected components. It provides a high-bandwidth communication channel for data transfer between various modules, allowing for scalability and flexibility in system design.

These are just a few examples of the different types of data bus found in computer systems. Each type serves a specific purpose and plays a crucial role in enabling efficient communication and data transfer within the system.

Address Bus vs. Data Bus

Within a computer system, both the address bus and the data bus play integral roles in the transfer of information between components. While they serve different purposes, their combined functionality is essential for the proper operation of the system. Let’s explore the key differences and functions of the address bus and the data bus:

Address Bus: The address bus is a unidirectional bus that carries memory addresses. Its primary function is to specify the location of data in memory during read or write operations. The processor uses the address bus to communicate with the memory and peripherals, transmitting the address of the data it wants to access. The width of the address bus determines the maximum memory capacity that the system can address. For instance, a 32-bit address bus can address up to 4 GB of memory. The address bus is essential for identifying and accessing specific data locations within the computer system.

Data Bus: In contrast, the data bus is a bidirectional bus that carries the actual data being transferred between components. It facilitates the parallel transfer of binary information, transmitting multiple bits of data simultaneously. The width of the data bus determines the number of bits that can be transferred at once. For example, an 8-bit data bus can transfer 8 bits of data in parallel, while a 16-bit bus can handle 16 bits simultaneously. The data bus allows for the flow of information between the processor, memory, and input/output devices. It is responsible for conveying the actual data during read, write, and transfer operations.

The key distinction between the address bus and the data bus lies in their functionality and the information they carry. The address bus carries memory addresses, specifying the location of data in memory. On the other hand, the data bus carries the actual data being transferred between components.

It’s important to note that the address bus and the data bus work together to enable efficient data transfer and communication within the computer system. The address bus helps the processor identify the location of the data, while the data bus allows for the actual transfer of the data between the identified locations.

Both buses are crucial and must be appropriately designed to ensure proper communication and data transfer within the system. The width of the buses, in terms of the number of lines or bits, directly influences the system’s performance and capacity. A wider data bus can transfer more data in parallel, while a wider address bus can address a larger memory space.

Width of Data Bus

The width of the data bus is a crucial characteristic that determines the amount of data that can be transmitted simultaneously between components within a computer system. It represents the number of lines or wires on the data bus and directly impacts the efficiency and speed of data transfer. Let’s explore the significance of the width of the data bus in more detail:

When we refer to the width of the data bus, we are essentially talking about the number of bits that can be transferred at a given time. For example, an 8-bit data bus can transfer 8 bits of data simultaneously, while a 16-bit data bus can handle 16 bits at once.

A wider data bus allows for parallel communication, which significantly enhances the efficiency and speed of data transfer within the computer system. Instead of transferring data bit by bit, parallel communication enables the simultaneous transfer of multiple bits, resulting in faster data transfers.

The width of the data bus is closely tied to the word length of the processor, which refers to the number of bits that the processor can process in a single instruction. The width of the data bus should ideally match the word length of the processor to ensure optimal performance. For example, if the processor has a 32-bit word length, it is advantageous to have a 32-bit data bus to match its capabilities.

Furthermore, the width of the data bus also impacts the system’s memory capacity. The width of the address bus determines the maximum memory that can be addressed, but the width of the data bus determines how much data can be transferred at once. A wider data bus allows for larger data transfers, increasing the system’s overall memory bandwidth.

It is important to consider the trade-offs associated with the width of the data bus. A wider data bus requires more lines and increased complexity in the system design, which can lead to higher costs and greater power consumption. Additionally, wider data buses are more susceptible to noise and signal degradation, potentially impacting the reliability of data transfer.

Therefore, when selecting the width of the data bus, it is essential to strike a balance between performance, cost, power consumption, and reliability considerations. The chosen width should align with the word length of the processor, memory requirements, and overall system architecture.

How Data Bus Works

The data bus plays a fundamental role in facilitating the transfer of data within a computer system. It acts as a communication channel that allows information to be exchanged between the central processing unit (CPU), memory, and input/output devices. Understanding how the data bus works is essential in grasping the intricacies of data transfer within a computer system. Here’s an overview of how the data bus operates:

1. Data Transmission: The data bus serves as a pathway for transmitting binary information in the form of electrical signals. These signals travel through a set of dedicated lines or wires, which represent bits of data. The data is transferred in parallel, meaning that multiple bits are transmitted simultaneously.

2. Timing and Synchronization: Data transfer on the data bus is controlled by a clock signal. This clock signal is generated by the system and sets the timing for data transmission. The clock signal ensures that data is transferred at uniform intervals and that the sending and receiving components are synchronized.

3. Bus Arbitration: In a multi-component system, where multiple devices may need to access the data bus simultaneously, bus arbitration protocols are employed. These protocols manage the access and prioritize the requests for bus usage, ensuring fair and efficient data transfer between the components.

4. Read and Write Operations: The data bus supports both read and write operations. During a read operation, the CPU or a peripheral device retrieves data from memory or another device by requesting the necessary address on the address bus and reading the corresponding data from the data bus. In a write operation, the CPU or peripheral device writes data to a specific address in memory or another device by providing the address on the address bus and placing the data on the data bus.

5. Data Integrity: To ensure the integrity of data during transmission, various error checking and correction mechanisms may be employed. These mechanisms detect and correct transmission errors that may occur due to noise, interference, or other factors. Checksums, parity bits, and error correction codes are examples of techniques used to maintain data integrity.

6. Bus Architecture: The data bus is typically organized in a hierarchical manner, with various levels of buffering and caching to optimize data transfer and system performance. Hierarchical bus architectures minimize data congestion and facilitate efficient communication between components.

Overall, the data bus enables the seamless flow of data within a computer system. It provides a pathway for parallel data transfer, synchronizes the operation of the components, and ensures data integrity. Understanding the workings of the data bus is essential for designing efficient and reliable computer systems.

Data Bus Capacity and Speed

The capacity and speed of the data bus play a crucial role in determining the performance and efficiency of data transfer within a computer system. The capacity refers to the amount of data that can be transferred at once, while the speed dictates how quickly the data can be transmitted. Let’s explore the significance of data bus capacity and speed in more detail:

Data Bus Capacity: The capacity of the data bus refers to the number of bits that can be transferred simultaneously. It is determined by the width of the data bus, which represents the number of lines or wires on the bus. A wider data bus can transfer more bits in parallel, increasing the data transfer rate.

Data Bus Speed: The speed of the data bus refers to the rate at which data can be transmitted. It is measured in bits per second (bps) or megahertz (MHz) and determines how quickly information can be exchanged between components. A higher data bus speed allows for faster data transfer, reducing latency and enhancing system performance.

The capacity and speed of the data bus are closely related, but they are not the same thing. While the width of the data bus determines its capacity, the speed determines how quickly the data can be transmitted across those lines.

It is important to note that the capacity and speed of the data bus impact the overall system performance, but they are not the sole factors affecting it. The performance is also influenced by other system components such as the processor, memory, and input/output devices.

When designing a computer system, it is essential to consider the data bus capacity and speed in relation to the requirements of the system. The selected width of the data bus should align with the processing capabilities of the system while considering the memory capacity requirements and the expected volume of data transfer.

The data bus speed should be balanced with the capabilities of the processor and memory to ensure optimal performance. The data bus’s speed must be compatible with the clock speed of the system and other components to avoid data bottlenecks and synchronization issues.

Advancements in technology have led to the development of faster and wider data buses, allowing for increased data transfer rates. High-speed serial interfaces, such as USB 3.0 and Thunderbolt, are examples of technologies that offer faster data rates by utilizing advanced signaling techniques.

Data Bus in CPU and Memory

The data bus plays a critical role in facilitating communication and data transfer between the central processing unit (CPU) and memory within a computer system. Understanding how the data bus is utilized in the CPU and memory subsystem is essential in comprehending the overall operation and performance of a computer system. Let’s explore the role of the data bus in these components:

Data Bus in CPU: Within the CPU, the data bus connects various internal components, including the arithmetic logic unit (ALU), registers, and cache memory. It allows for the flow of data between these components during processing operations. For example, when performing arithmetic calculations, the data bus transfers the relevant numerical values between the ALU and registers. The width of the data bus determines the maximum data capacity that can be processed by the CPU, affecting its computational capabilities and overall performance.

Data Bus in Memory: In the context of memory, the data bus is responsible for the transfer of data between the CPU and the different types of memory, such as RAM (Random Access Memory) and ROM (Read-Only Memory). The data bus provides the pathway through which the CPU reads instructions and data from memory, as well as writes data back to memory. It enables the quick retrieval and storage of data required for program execution. The width of the data bus influences the maximum amount of data that can be read from or written to memory in a single operation, impacting memory access speed and overall system performance.

It is essential to ensure compatibility between the data bus in the CPU and memory subsystem. The width and speed of the data bus in the CPU and memory should be adequately matched to allow for efficient communication and data transfer. Mismatched data bus configurations can result in inefficiencies, such as data bottlenecks, limited memory access, and reduced system performance.

Modern computer systems often feature multi-level caching mechanisms that utilize dedicated data buses to improve system performance. These caches, such as L1, L2, and L3 caches, store frequently accessed instructions and data closer to the CPU to reduce memory access latency. The data bus connections between the CPU and cache memory play a critical role in ensuring rapid retrieval and storage of data, further enhancing system performance.

Overall, the data bus is a key component that facilitates the transfer of data between the CPU and memory within a computer system. It enables efficient communication and data exchange, contributing to the overall operation and performance of the system. By ensuring compatibility and optimal configuration of the data bus in the CPU and memory subsystem, system designers can enhance the functionality and efficiency of the computer system.

Limitations of Data Bus

While the data bus plays a vital role in facilitating data transfer and communication within a computer system, it comes with certain limitations that can impact system performance and functionality. Understanding these limitations is important for system designers to make informed decisions about system architecture and design. Here are some common limitations of the data bus:

1. Bandwidth Constraints: The width of the data bus determines its maximum capacity for transmitting data. This limitation can result in bandwidth constraints, especially when dealing with large volumes of data or high-speed data transfers. In scenarios where the data bus becomes a bottleneck, it can lead to decreased system performance and slower data transfer rates.

2. Signal Degradation: As data is transmitted through the data bus, it can be susceptible to signal degradation caused by factors like noise, interference, or line capacitance. Signal degradation can introduce errors, leading to data corruption and decreased reliability. Signal integrity techniques, such as shielding and error detection mechanisms, need to be employed to mitigate signal degradation issues.

3. Synchronization Challenges: The data bus operates based on a clock signal to ensure synchronized data transfer. However, as system complexity increases, synchronization challenges can arise. Different components may operate at varying speeds, leading to timing mismatches and potential data synchronization issues. Proper clocking mechanisms and synchronization techniques are necessary to mitigate these challenges.

4. Limited Scalability: The scalability of the data bus can be a limitation in systems that require significant expansion or future upgrades. Adding more components or increasing the data transfer requirements may exceed the capacity of the existing data bus. In such cases, upgrading or redesigning the data bus architecture becomes necessary to accommodate the increased demands of the system.

5. Power Consumption: A wide and high-speed data bus can consume significant power, contributing to the overall power requirements of the system. This can be a limitation in systems with strict power constraints, such as mobile devices or battery-powered systems. Balancing the performance benefits of a wider data bus with the power consumption limitations is crucial in such scenarios.

6. Physical Constraints: The physical implementation of the data bus can also introduce limitations. Physical constraints such as wire length, resistance, and capacitance can affect data transmission characteristics, leading to signal distortion and degradation. Proper consideration of physical design factors is essential to mitigate these constraints.

System designers must carefully assess these limitations to design data bus architectures that optimize performance, reliability, and scalability. Mitigating these limitations often involves employing techniques such as parallel bus interfaces, error detection and correction mechanisms, clock synchronization, and advanced physical signal integrity measures. By understanding and addressing these limitations, system designers can overcome potential obstacles and maximize the efficiency and effectiveness of the data bus within a computer system.

Future Developments in Data Bus Technology

Data bus technology is constantly evolving to meet the growing demands of computer systems in terms of data transfer speed, capacity, and efficiency. As technology continues to advance, several developments are expected to shape the future of data bus technology. Here are some potential future developments:

1. Increased Data Bus Width: One of the key areas of development is the expansion of data bus width. Wider data buses allow for greater parallelism and higher data transfer rates. Future systems may feature wider data buses, such as 32-bit, 64-bit, or even wider, enabling even faster data transfer and improved system performance.

2. Higher Data Bus Speeds: Advancements in signaling and transmission technologies are expected to lead to higher data bus speeds. This can be achieved through the use of advanced transmission protocols, better cabling, and signal integrity enhancement techniques. Higher data bus speeds will further enhance the overall performance and responsiveness of computer systems.

3. Serial Bus Interfaces: Serial bus interfaces, which transmit data bit by bit in sequence, have gained popularity due to their advantages in terms of longer cable lengths, simplified wiring, and scalability. Future developments may see increased adoption of serial bus interfaces, such as USB Type-C and Thunderbolt, in various applications to support high-speed data transfer and connectivity.

4. Advanced Error Detection and Correction: To ensure reliable data transfer, future data bus technologies may incorporate more advanced error detection and correction mechanisms. These mechanisms can help identify and correct transmission errors, ensuring data integrity during transfer and reducing the potential impact of noise or interference.

5. Optics-Based Data Communication: Optical communication, which utilizes light signals instead of electrical signals, holds tremendous potential as a future data bus technology. Optical data communication offers advantages such as high bandwidth, immunity to electromagnetic interference, and lower power consumption. Ongoing research aims to develop optical data bus solutions capable of efficiently transmitting data over longer distances and within complex computer systems.

6. Integration of Data and Power Buses: Combining data bus and power bus functionalities into a single interface can enhance system efficiency and reduce complexity. This integration can lead to more streamlined designs, eliminating the need for separate power connections and reducing overall system cabling. Future developments may explore such integrated data and power bus solutions.

7. Enhanced Scalability and Flexibility: As computing requirements continue to evolve, future data bus technologies will focus on improving scalability and flexibility. This includes designing data bus architectures that can support seamless system expansion and the integration of new components as technology advances. Scalable data bus designs will allow for easy upgrades and enhancements without requiring extensive hardware modifications.

These are just a few potential future developments in data bus technology. As the demand for higher data transfer speeds, increased capacity, and improved efficiency persists, researchers and engineers will continue to explore innovative solutions to push the boundaries of data bus technology, enabling more powerful and advanced computer systems in the future.